算力航母:英特尔展示18A工艺AI芯片

独家抢先看

IT之家 1 月 31 日消息,英特尔代工服务(Intel Foundry)本周发布技术文档,展示“AI 芯片测试载具”,用于验证其在先进封装领域的制造能力。

IT之家援引博文介绍,测试载具(Test Vehicle)并非是指最终上市销售的商品,而是为了验证制造工艺、设计思路是否可行而制造出来的“工程样机”,就像汽车厂商发布的概念车或测试车。

根据技术文档,该测试载具的系统级封装(SiP)拥有 8 倍光罩尺寸,内部集成了 4 个大型逻辑计算单元(Logic Tiles)、12 个 HBM4 级别的内存堆栈以及 2 个 I/O 单元。

值得注意的是,与上月展示的“16 逻辑单元 +24 内存堆栈”的概念模型不同,本次展示的方案代表了英特尔目前已实际具备的量产制造能力。

在核心工艺上,该测试平台的核心逻辑单元采用了英特尔最先进的 18A 工艺,集成了 RibbonFET 全环绕栅极晶体管和 PowerVia 背面供电技术。

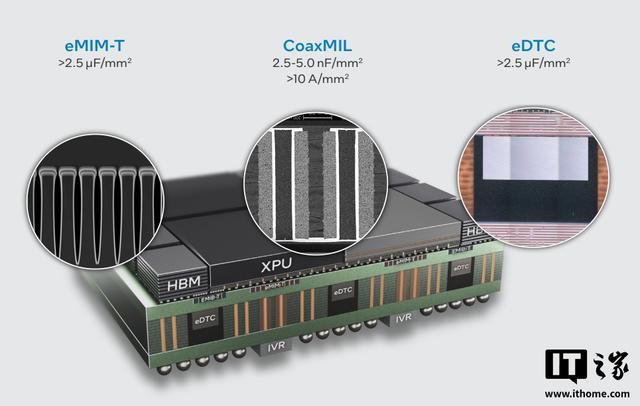

在芯片互连方面,英特尔采用了 EMIB-T 2.5D 嵌入式桥接技术。通过在桥接器内部添加硅通孔(TSV),电力和信号不仅可以横向传输,还能实现垂直传输,从而最大化互连密度,设计支持高达 32 GT/s 的 UCIe 接口标准。

芯片堆叠方面,英特尔将利用 Foveros 3D 封装技术(包括 Foveros 2.5D、Foveros-R 和 Foveros Direct 3D)实现垂直堆叠芯粒(Chiplets),底层的 18A-PT 基础芯片(Base Dies)位于计算芯片下方,可充当大容量缓存或处理额外任务。

供电方面,英特尔将支持支持“Semi”集成电压调节器(IVR),并利用嵌入式同轴磁性电感器(CoaxMIL)和多层电容网络(如 Omni MIM),集成全套供电创新技术。

与台积电 CoWoS-L 将电压调节器置于中介层不同,英特尔将其置于每个堆栈及封装下方。这种设计旨在应对生成式 AI 负载产生的瞬时电流波动,确保在不损失电压余量的情况下提供清洁、稳定的电力。

“特别声明:以上作品内容(包括在内的视频、图片或音频)为凤凰网旗下自媒体平台“大风号”用户上传并发布,本平台仅提供信息存储空间服务。

Notice: The content above (including the videos, pictures and audios if any) is uploaded and posted by the user of Dafeng Hao, which is a social media platform and merely provides information storage space services.”