台积电1.6纳米制程2026年底量产:带来了哪些改进与新挑战?

独家抢先看

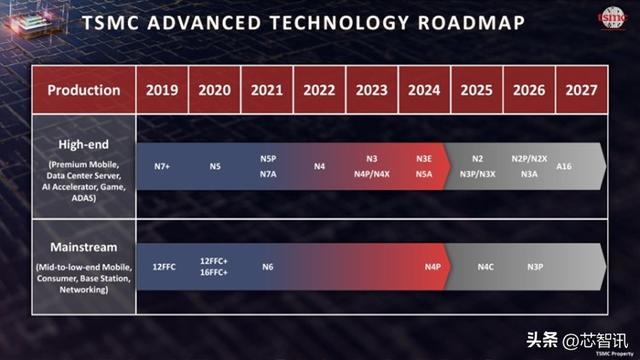

11月23日消息,据Tom's hardware报道,近日台积电在荷兰阿姆斯特丹举行的欧洲开放创新平台 (OIP) 生态系统论坛上宣布,该公司未来几年的计划基本保持不变,将于 2025 年底开始量产 N2(2 纳米级)制程,并于 2026 年底量产 A16(1.6 纳米级)制程。

台积电设计基础设施管理主管 Dan Kochpatcharin 表示:“您在这里看到的路线图与六个月前的技术研讨会上看到的技术路线图相同。我们有 N2、N2P,它们将于明年和后年投入生产。接下来是2026年底量产的A16。”事实上,所有这些工艺技术都计划在 2026 年底投入大批量生产 (HVM)。

从技术上讲,N2、N2P、N2X 和 A16 有很多相似之处:它们都基于全环绕栅 (GAAFET) 纳米片晶体管。其中,N2 系列使用超高性能金属绝缘体金属 (SHPMIM) 电容器来降低晶体管通孔电阻以提高性能效率,而 A16 将使用台积电的超级电轨 (SPR) 背面供电网络 (BSPDN) 来进一步改进它。

N2P它比典型的 N2 提高了性能,但它不会增加与背面供电相关的复杂性,这对于客户端设备(例如智能手机和入门级 PC 的片上系统 (SoC))来说是最佳选择。当然,N2X 通过增加更高的电压进一步提高了性能,这可能对各种应用(例如高性能 CPU)都有好处。

A16的BSPDN技术可实现增强的供电,将所有电力路由到芯片的背面,并实现更高的晶体管密度。虽然这个 BSPDN 解决了一些挑战,但它也增加了其他挑战,因此需要额外的设计工作。

正如台积电设计解决方案探索总监 Ken Wang 所指出的,“天下没有免费的午餐”。背面供电也增加了必须缓解的散热问题。当前实施的 BSPDN 最适合数据中心级 AI 处理器,而台积电目前瞄准的正是 A16 所针对的细分市场。

与N2P制程相比,台积电承诺A16在相同的电压和复杂性下性能提高 8%-10%,或者在相同的频率和晶体管数量下降低 15%-20% 的功耗。此外,台积电估计高端 AI 处理器的芯片密度将是之前的 1.07 倍至 1.10 倍,具体取决于所使用的晶体管类型和库。

台积电设计解决方案探索和技术基准测试部门总监 Ken Wang 表示,从架构上讲,A16 晶体管类似于 N2 晶体管。这简化了从 N2 到该工艺技术的迁移。

“从 N2P 到 A16 的逻辑布局迁移实际上非常简单,因为单元结构和大多数布局模式都非常相似,”Ken Wang说。“因此,除了保持相同的正面结构外,A16 的美妙之处在于它继承了 N2 器件宽度调制的 NanoFlex 功能,以实现最大的驱动力。”

台积电的超级电轨技术通过专用触点将背面供电网络直接连接到每个晶体管的源极和漏极,从而最大限度地减少导线长度和电阻,从而最大限度地提高性能和电源效率。在生产方面,这种实现是最复杂的 BSPDN 设计之一,超过了英特尔的 Power Via 的复杂性。

然而,先进的 BSPDN 实现也意味着芯片设计人员必须完全重新设计他们的供电网络,以新的方式进行布线。因此,应用新的布局布线策略,这是意料之中的。此外,他们必须进行一些热缓解,因为芯片的热点现在将位于一组线路下,从而使散热更加困难。

使用BSPDN设计芯片本质上意味着随着许多事情的变化而采用新的实现方法,包括设计流程本身。Ken Wang提到了新的热感知布局布线软件、新时钟树结构、不同的 IR-Drop 分析、不同的电源域和不同的热分析核签等的使用。

考虑到新的实现流程,需要新版本的 EDA 工具和仿真软件。由于A16是类似于台积电的 N2 的节点,因此许多事情都已准备就绪,即便是在 Cadence 和 Synopsys 等领先制造商的之前0.5版本的 EDA 工具中。

“A16 是一种适用于具有复杂路线和密集 PDN (供电网络)的设计的技术,”Ken Wang说。“然而,它也带来了新的挑战,因此需要额外的设计工作。我们的背面触点 VB 也需要勤奋地进行完整的芯片验证。与此同时,我们有一个全面的 A16 EDA 支持计划,该计划正在进行中,我们将继续更新 A16 EDA 状态。”

编辑:芯智讯-浪客剑

“特别声明:以上作品内容(包括在内的视频、图片或音频)为凤凰网旗下自媒体平台“大风号”用户上传并发布,本平台仅提供信息存储空间服务。

Notice: The content above (including the videos, pictures and audios if any) is uploaded and posted by the user of Dafeng Hao, which is a social media platform and merely provides information storage space services.”